-

Notifications

You must be signed in to change notification settings - Fork 747

New issue

Have a question about this project? Sign up for a free GitHub account to open an issue and contact its maintainers and the community.

By clicking “Sign up for GitHub”, you agree to our terms of service and privacy statement. We’ll occasionally send you account related emails.

Already on GitHub? Sign in to your account

Porting OpenJ9 to RISC-V #5058

Comments

|

@shingarov you might be interested in this one :) |

|

Currently, I already finished the following jobs:

|

|

@pshipton , I am wondering whether we should disable the shared classes on the resource-limited board (only 128M flash memory available for use, which includes the Linux port/utilities, the Java build, user applications, etc) as the shared cache is set to 300M by default. In addition, we might need to disable some modules/unnecessary stuffs in code to get things easy to go on the board. |

|

@ChengJin01 |

|

Probably need to disable these modules in config/setting in the OpenJDK before compiling the build with riscv32 as there might be no way to run jink on the compiled build (all executables are already in the RISC-V format) on the host machine. |

|

@ChengJin01 When the available disk space is small, the default shared cache size should be 64MB. However I can guess this still might be too big. We do want to ensure shared classes is working, and could set an even smaller size for this platform, like 16M or even 4M just for test purposes. |

|

Actually, this is 32-bit, so the default shared cache size should be 16MB already. The 300MB default size is for 64-bit only. |

|

I doubled-check the document on HiFive1(32bit FE310), it is actually 16MB off-chip flash memory (128Mbit). So the shared cache still needs to be reduced if possible. In addition, according to the technical Spec on FE310 at and the discussion of Linux port on HiFive1 at https://forums.sifive.com/t/is-there-a-linux-distribution-that-can-run-on-hifive1/658/5, it seems the 32bit FE310 chip holds a very tiny RAM (16KB) which is far from enough to support the Linux kernel. Given that porting OS kernel to the board is not our focus, there might be two options for us to move forward:

|

|

|

Surely supporting the shared classes cache could be considered on the "nice to have" list rather than in the initial set of priority activities for a new platform bring up? Is there an existing new platform bring-up (ordered) checklist? If not, could we start creating one as part of this effort? |

There is no public doc/Spec shows it can do that but we can bring this question to their forum at https://forums.sifive.com. (already raised the question at https://forums.sifive.com/t/extending-the-hifive1-board-with-additional-ram-disk/2155)

The typical emulator is QEMU (https://github.com/riscv/riscv-qemu) both with RISC-V (RV64G, RV32G) Emulation Support. It will be used to boot the Linux/shell so as to run the JVM after compilation.

In this case, there might be not too many options in term of development boards except the 64bit HiFive FU540 Unleashed board. Technically, most of work will be finished (compilation, emulation, etc) before uploading everything to the board which should be the final steps to verify whether it really works on the RISC-V chip/hardware. So it might be not that urgent for the moment to decide which board to use as long as we get our build work on RISC-V via emulator. |

|

Already talked to @mstoodle on slack, we can create a high-level/generic porting guideline not specific to any platform with our porting experiences on RISC-V, which helps people to understand the basic/key steps to follow when porting OpenJ9 to a new platform. |

@knn-k has some recent experience porting OpenJ9 onto Aarch64. He might be helpful regarding the porting guideline. |

|

If it is without the JIT, you can take a look at these PRs to begin with for what I have done with AArch64 VM build:

|

|

@knn-k , many thanks for your links of changsets. I believe we will get started with at least something similar (with RISC-V instruction sets) except Docker-related stuff as we need to run it directly on hardware/board. |

|

AArch64 VM uses the Docker image for cross-compilation on x86-64 Linux. |

|

[1] The response as to extending the 32bit board with external RAM/disk as follows: So it seems extending the hardware this way is tricky and it is hard to say whether the 32bit board can really support that. [2] I went over the Spec document for the 64bit board at https://sifive.cdn.prismic.io/sifive%2Ffa3a584a-a02f-4fda-b758-a2def05f49f9_hifive-unleashed-getting-started-guide-v1p1.pdf, If it is the mainstream hardware setup on the 64bit board, there should be no limitation [3] There are 3 options for the cross-compilation & EQMU emulation:

I will go with the option 1) to compile everything including EQMU, which is the fastest & straightforward way we can do to solve all problems on our side before moving forward to the on-board/hardware verification. If there is any special configuration/setting required in the boot process on the hardware which can't be done via 1), I will go back to check whether 2) or 3) works that way. |

|

Already created the RISC-V cross compiler on 64bit: Will keep compiling other related artifacts. |

|

Hello, I would like to add some comments. First off I am a large contributor to meta-riscv and the Yocto/OpenEmbedded world in general. Please let me know what you need and I will help wherever I can. The less time you all spend on getting Linux running the more time you can spend on porting Java :) Please do not spend time on the HiFive1 board OR 32-bit RISC-V. The HiFive1 board is very small, it's basically a RISC-V version of an Arduino. RISC-V 32-bit support is still lacking so you should start with 64-bit support. You can develop for 64-bit RISC-V on either the HiFive Unleashed or QEMU. QEMU has great RISC-V support and you should be able to do all your development on QEMU. If you want help running QEMU please let me know, I am also a QEMU maintainer and am happy to help here as well. I think meta-riscv is the best option from above to use (option [3]). It's extremely powerful and you won't have any issues of size in either QEMU or on the HiFive Unleased. Buildroot is also an option (as a maintainer here as well I can help if required). I would not recommend to build it all yourself, you will end up wasting a lot of time building toolchains, Linux and related packages. |

|

If you want to do native work you can also just run Fedora on QEMU and dnf install all the packages you need. Either way, let me know how to help and I will do what I can |

|

Something else worth noting is that most of the repos on the github riscv account are out of date. For Linux, GNU tools and QEMU you should use mainline not the riscv forks. |

|

@alistair23 , many thanks for your suggestion & recommandation. Actually I already finished compiling everything on 64bit including QEMU with option 1) (just a minor issue with ntpd which can be ignored for now). We will move forward to the next step to compile our code if everything goes fine. The problem with option [3] is it will end up with a huge size of linux image which I already tried but stopped it when it exceeded 9GB (What we need is a normal Linux kernel with decent shell support, so there is no need to integrate everything for Linux). With option 1, we are able to customize the size for use (e.g. 1GB or less if necessary). I won't go for option 2) or 3) for now unless there is something unexpected when compiling our code. |

|

Great, I'm glad you got it working! I'm not sure how you eneded up with a 9GB image, my full OpenEmbeded desktop images with debug symbols and self hosted toolchains aren't that big. Either way can you keep me updated with the progress? Also let me know if there is anything that I can do to help. |

|

@alistair23 , I didn't try other options except Basically the compilation of our code will be done with the 64bit cross-compiler outside of QEMU and mount the whole build inside to get executed in there. So we definitely need your support from QEMU perspective. My guess is there will be a bunch of problems with QEMU once we're done compiling our code to get it work, specifically in debugging in QEMU if it crashes or something similar happens. Just keep subscribed in this issue and you will be informed with what is going on in our project. |

|

Ah, the temporary files can get big. That makes more sense. Great! I am subscribed to this issue so I will keep and eye on things and help where I can. QEMU is very stable and the RISC-V support is also mature. If possible it would be best to build it from the master branch in mainline QEMU. Otherwise the 3.1+ releases are in good shape. Good luck with this. Java is one of the few missing pieces for RISC-V so it will be great when you get it running :) |

|

Working on other crash issue on Windows. Will get back to this once we address that problem. |

|

I am currently compiling a build without JIT components (excluded from OpenJ9 & OMR) on a Fyre Linux machine and then on my Ubuntu VM to eliminate any compilation error with JIT excluded. If it works good, the next step is to get the risc-v toolchain introduced in the configure/setting to see what happens (temporarily ignore the spec setting & code specific to riscv and just ensure it picks up the correct cross-compiler/tools in the process of compilation) |

|

I've finished all the minimal openjdk_tests (including the jdk_lang & jdk_pack200) with the cross-build on Debian_riscv/U540 and no risc-v specific issue was detected except a couple of timeout cases, some of which I already verified with a single run and all of them passed. I will get started to check the DDR related tests on the native build (compiled on Fedora_raw/QEMU) to ensure everything works fine. |

|

Just finished the DDR related tests with the native build on Will get back to keep investigating the exception issue with |

|

To figure out what happened to |

|

Currently investigating an issue with the code of checking the qualified name in loading classes. Will get back to this once the problem there gets addressed. |

|

@ChengJin01

I'll do further debugging in GDB later. |

|

@janvrany , Many thanks for the investigation from Debian_riscv. Given that the latest kernel version of Fedora_raw is but it seems the old version only support QEMU rather than hardware. So if the single step debugging works good on |

That's exactly the plan :-) |

However, the debugging result at debug_debian_String_clinit_log.TXT didn't indicate there was any

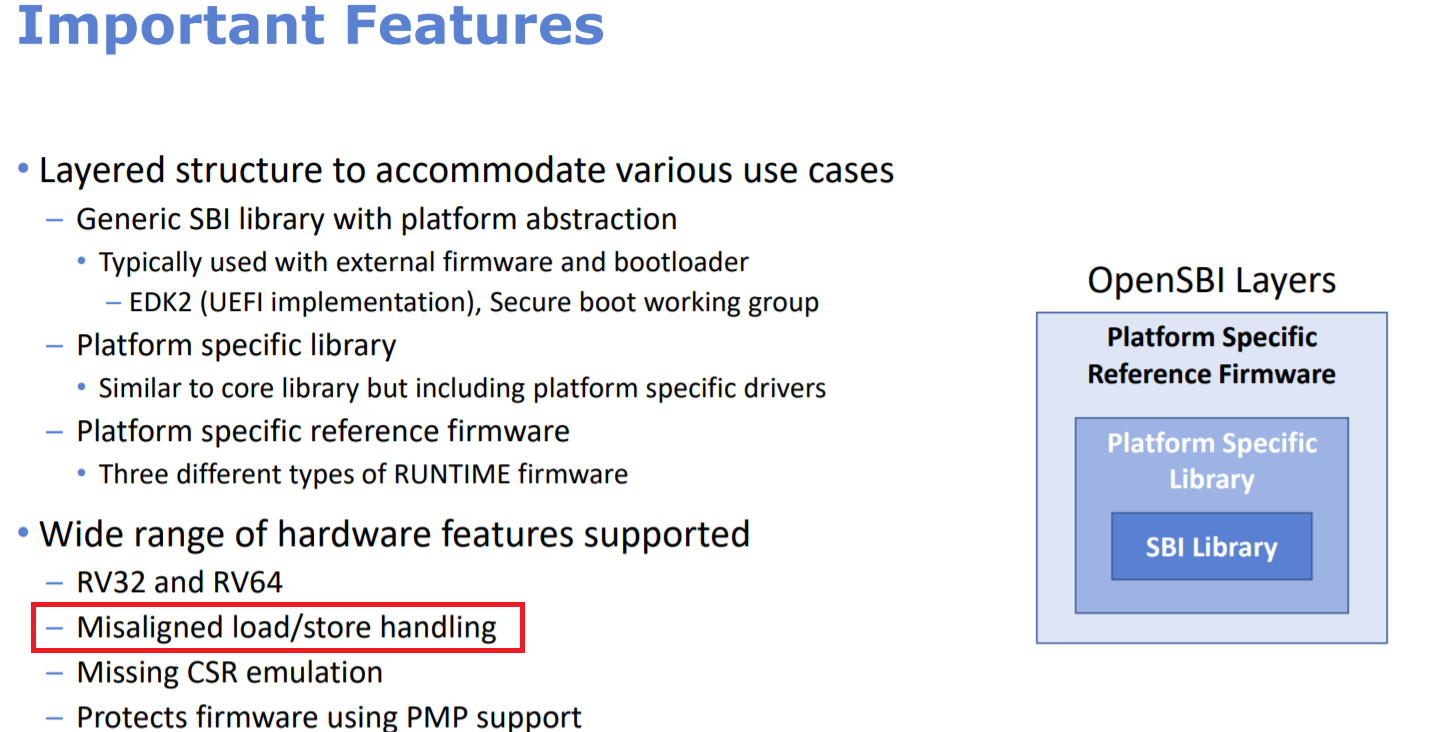

against the publicized plus the explanation of OpenSBI (replacing BBL in the booting flow) at https://content.riscv.org/wp-content/uploads/2019/12/Summit_bootflow.pdf I suspect |

|

I tried So there is no way to know whether against the output of Linux kernel vesion on Given that |

|

@ChengJin01 As you can see, At first glance, none of the values look like object reference. I'll continue digging. |

|

Hi @janvrany, Many thanks for your debugging on the latest version of Debian on U540. If the crash literally happened to the code near to So I will burn the image to SD-card and repeat your steps to generate a debug build and double-check the result to see whether the crash still occurs around there before moving forward. |

|

@ChengJin01: just in case you would find that useful: here are my scripts to (reproducibly) compile debug build of OpenJ9 on RISC-V Debian: https://github.com/janvrany/openj9-openjdk-jdk11-devscripts |

|

After attempting a bunch of times, I managed to get Debian with Linux kernel 5.6 working on U540 The next step is to generate a couple of builds (including the debug build) to see how it goes with the latest linux kernel + OpenSBI. |

|

I am currently setting up the test environment for the internal tests on Debian(5.0) with BBL/U540. Will get back to the investigation on the latest linux kernel + OpenSBI after the test is completed. |

|

@ChengJin01 Hi Cheng Jin, By following your instruction I have built a jdk image and successfully run I searched issues and have no idea about enabling openJ9 JIT on RISCV64 yet. Could you have any plan on openJ9 JIT and a new long-term roadmap instead of #5058? Thank you for your advice. |

|

Hi @zdlgv5, Many thanks for your support on the OpenJ9/RISC-V project! As for the OpenJ9 JIT on RISC-V, it is already on our priority list but we have not yet get started for now coz there are some details we need to figure out as to what is best way to move forward. Please stay tuned! FY: @0xdaryl |

|

Hi, @zdlgv5, I'm currently doing some preparatory work to start working on OpenJ9 part of the JIT and hoping to start doing some real JIT work soon (TM) |

|

Hi, @ChengJin01 and @janvrany , |

|

For those of you who are concerned about the latest status of OpenJ9 JIT on RISC-V, the issue at #11136 was created to track the progress in there. |

|

The investigation with while it works good on the 5.0 + BBL to jump to the right path as follows: It doesn't mean After discussing with the Western Digital Developers working on Linux kernel & OpenSBI, they concluded that the problem came from the code with sign-extending in OpenSBI at https://github.com/riscv/opensbi/lib/sbi/sbi_misaligned_ldst.c: and committed a new fix for the issue two weeks ago at riscv-software-src/opensbi@7dcb1e1 @janvrany (our partner) just verified on Debian 5.6 + the patched OpenSBI v0.6 with the fix above and The next steps include:

|

|

Any opinions on whether we ought not to rely on support for misaligned accesses like that? Perhaps there's some performance benefit to be had? |

|

@keithc-ca , OpenSBI is the standardized binary interface (aimed to replace BBL as a new kind of BIOS on RISC-V) intended for all OS images & hardware on RISC-V (see https://github.com/riscv/opensbi & https://riscv.org/wp-content/uploads/2019/06/13.30-RISCV_OpenSBI_Deep_Dive_v5.pdf) If we chose not to reply on the fix from OpenSBI, there might be a bunch of code changes everywhere in the interpreter except and there is no way to to determine what happens next in the code depending on where the unaligned load/store opcode is placed in assembly (it could happen anywhere in our code except the interpreter). (The reason for this is that the underlying hardware doesn't support misaligned load/store which is why OpenSBI comes for help) https://riscv.org/wp-content/uploads/2019/06/riscv-spec.pdf I am not sure whether it benefits from any change specific to RISC-V in the interpreter but the first thing comes to my mind is the unexpected behaviour anywhere afterwards which will be extremely difficult in troubleshooting. |

|

This is the key point in the spec:

Notice it says 'may', not 'must'. As it is, it would seem our VM will simply not run on an EEI that doesn't support misaligned memory accesses. |

Yes to some extent, which is why OpenSBI needs to address all related misaligned memory accesses from the hardware. Given the code is shared across various platforms and the problem never happens on other platform & hardware except RISC-V, I don't see there is any special reason to handle this situation specific to RISC-V on our side (I kind of doubt whether it can be totally fixed simply by modifying the code above in the interpreter as there might be something else we are unaware of in other code in terms of generated assembly). |

|

For now, I would say that we can only run on systems which allow misaligned access. I'd rather not pollute the code with macros unnecessarily. |

|

Even on systems that allow misaligned access, there may be a performance penalty, but until any such penalty is quantified, I agree we should leave the code alone. |

|

With a newly created Debain5.6 + patched OpenSBI (fix upstreamed to https://github.com/janvrany/riscv-debian/tree/linux-5.6 by @janvrany), I verified our build works good as expected on U540 as follows: Will set up the test environment on U540 to do internal tests to see whether everything still goes fine with the new fix. |

|

I finished the internal tests which worked good on Debain5.6 + patched OpenSBI. Will wait for the new version of Fedora_riscv to double-check. |

|

hi this is abhishek here ,i am trying to port openjdk to riscv and i am facing problem in native compile can you help me to share the steps what to followed,thanks in advance |

|

@abhishekece : are you asking about the OpenJ9 JVM on RISC-V, or OpenJDK? OpenJDK-specific questions about RISC-V are best asked at the OpenJDK project. However, if you're asking about OpenJ9, please describe your problem in more detail. |

We determined to port a complete runtime environment including OpenJDK11 + OpenJ9 + OMR (without JIT) to the RISC-V development board (e.g. HiFive Unleashed with Linux support / please refer to https://www.sifive.com/boards/hifive-unleashed for details) to get it work on the board.

According to the explanation of RISC-V cross-compilers at https://www.lowrisc.org/docs/untether-v0.2/riscv_compile/, the JDK /JRE is supposed to be executed with Linux support in the user mode as the JVM /application is multiple-threaded.

Overall, there are a bunch of prerequisites before compiling OpenJ9:

Considering the complexity & unexpected challenges during the porting, the project will be split into at least 4 sub-tasks as follows to be accomplished to achieve our goal:

The issue at #11136 was created separately to track the progress of OpenJ9 JIT on RISC-V.

Another issue at #12699 for the CI pipline environment setup.

FYI: @DanHeidinga , @pshipton, @tajila

The text was updated successfully, but these errors were encountered: